BACKGROUND

Advanced Encryption Standard or AES is designed to encrypt and decrypt data using the same key. Given a segment of data, AES will use a key to encrypt the data in a way that is reversible only if the same key is given to the decryption algorithm. AES is widely adopted and standardized by the National Institute of Standards and Technology and provides secure point-to-point communication for a wide range of devices such as Wireless Routers, Chip to Memory Communication, Storage Encryption, and many more. This type of encryption is referred to as “Symmetric” Encryption, a good analog for this encryption is a safe with a combination lock. In order to both place information in the safe (Encrypt) and get information out of the safe (Decrypt) the same combination is used.

SUMMARY OF TECHNOLOGY

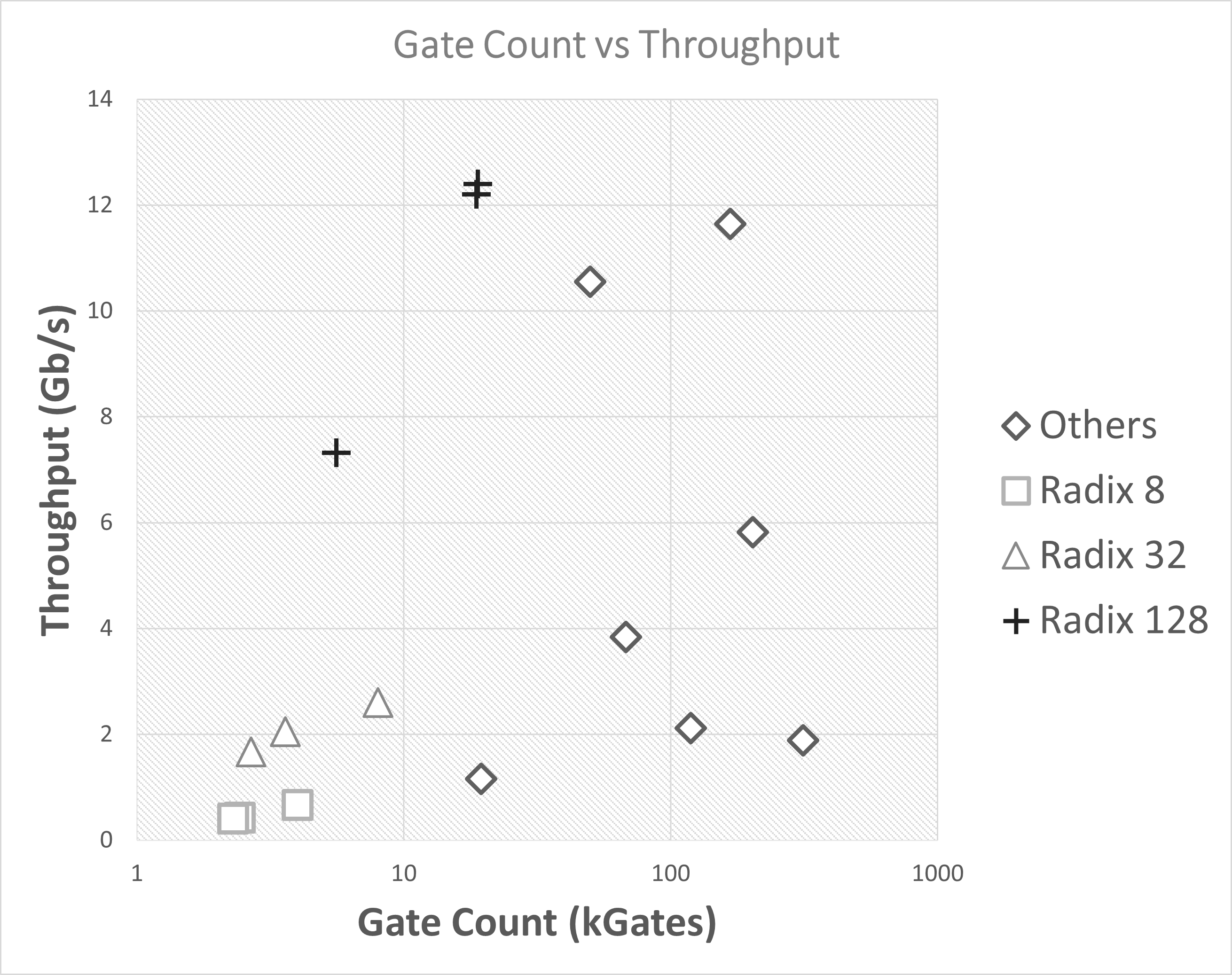

With the widespread usage of AES in high-performance applications such as networking, efficiency is more important than ever. However, due to processing limitations, it is not always feasible to reach the speeds required for specific applications of the technology. Our technology provides a solution for increased encryption performance such that higher speeds can be achieved for AES encryption. To summarize, the AES data encryption algorithm performs four operations on a set of data, Shift Rows, Substitution, Mix Columns, and Add Round Key. Due to the type of computation involved the most time additive components are the two in the center, Substitution, and MixColumns. There are many different methods for the implementation of these algorithms, however, our design provides a significant performance improvement by combining the separate lookup components in MixColumns and Substitution into a single lookup component. This allows for more efficient execution of the algorithm in many use cases. In the inventors’ experimentation, the application of this technique provided a 10% reduction in the critical path of the design utilizing industry standard tools compared to a base implementation which is identical other than the proposed technology.

POTENTIAL AREAS OF APPLICATION

- Networking Technology (Routers, Switching Fabric, etc.)

- Secure Integrated Circuit Inter-communication

- Secure Processor to Memory communication protocol

- AES Application Specific Integrated Circuits

MAIN ADVANTAGES

- Decreased Critical Path and computation complexity for AES Encryption

- Increased throughput of AES operation

STAGE OF DEVELOPMENT

A working model is available.

INTELLECTUAL PROPERTY

A patent application has been filed

LICENSING CONTACT

Contact jair@okstate.edu for more information.